# INTEGRATED CIRCUITS

Product specification

1996 May 01

Data Handbook IC20

### **TPM749**

#### DESCRIPTION

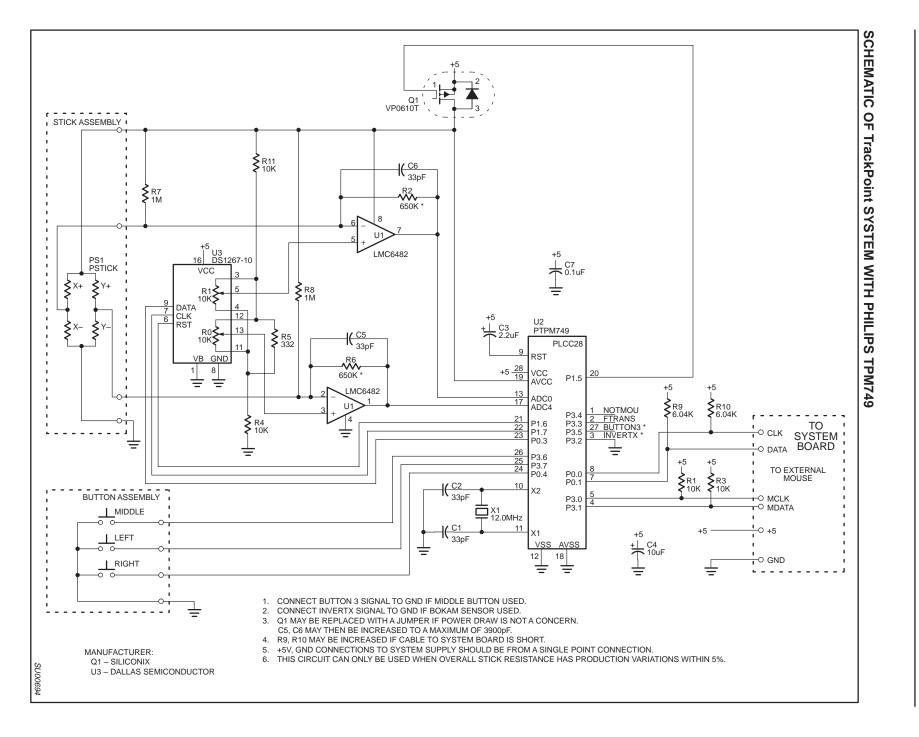

The Philips Semiconductors TPM749 is a small package, low cost, ROM-coded 80C51 with IBM®'s TrackPoint™ pointing algorithms and control code. TrackPoint is the result of years of human factors research and innovation at IBM. The result is a "velocity sensitive" pointing solution more efficient and easier to use than "position sensitive" devices such as the mouse, the trackball, or the touchpad.

IBM has licensed Philips Semiconductors to sell microcontrollers with TrackPoint code. By purchasing a TPM from Philips, the purchaser becomes a sub-licensee of Philips. The selling price of Philips' TPM includes the royalties for IBM's intellectual property, which Philips in turn pays to IBM. Customers for TPMs do not need to sign any licensing agreement with either IBM or Philips. This code is the intellectual property of IBM, which is covered by numerous patents, and must be treated accordingly.

The TPM is fabricated with Philips high-density CMOS technology. Philips epitaxial substrate minimizes CMOS latch-up sensitivity.

The TPM contains a  $2k \times 8$  ROM, a  $64 \times 8$  RAM, 21 I/O lines, a 16-bit auto-reload counter/timer, a fixed-priority level interrupt structure, an on-chip oscillator, a five channel multiplexed 8-bit A/D converter, and an 8-bit PWM output.

The TPM supports two power reduction modes of operation referred to as the idle mode and the power-down mode.

#### FEATURES

- 80C51 based architecture

- Small package sizes

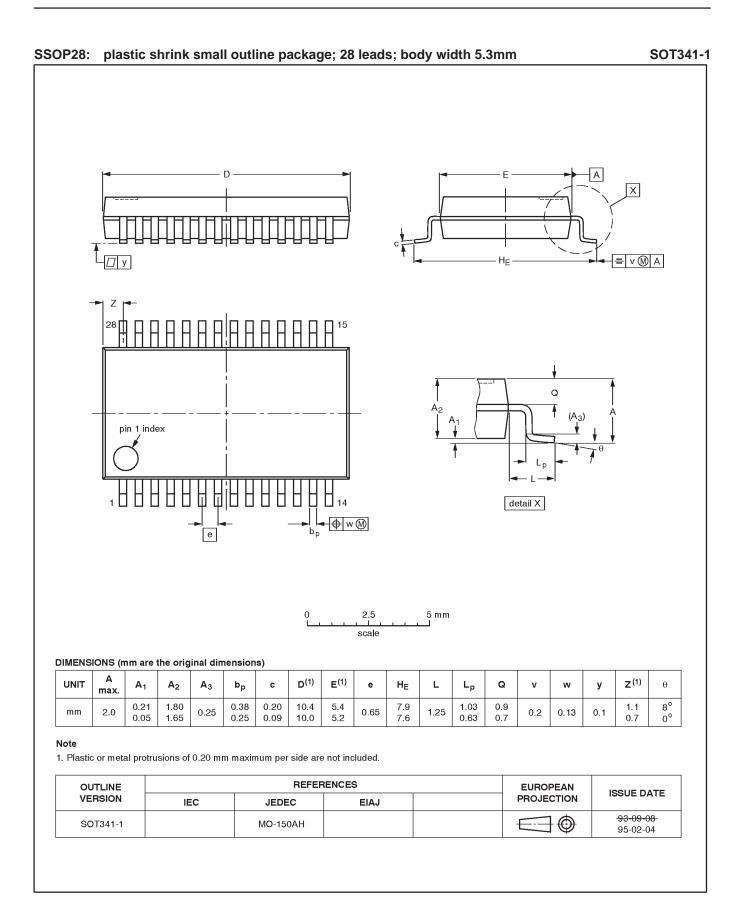

- 28-pin Shrink Small Outline Package (SSOP)

- 28-pin PLCC

- Low power consumption:

- Normal operation: less than 11mA @ 5V, 12MHz

- Idle mode

- Power-down mode

- 2k × 8 ROM

- 64 × 8 RAM

- 16-bit auto reloadable counter/timer

- 5-channel 8-bit A/D converter

- 8-bit PWM output/timer

- 10-bit fixed-rate timer

- CMOS and TTL compatible

#### **ORDERING INFORMATION**

| ORDERING CODE | ORDERING CODE TEMPERATURE RANGE AND PACKAGE |          |

|---------------|---------------------------------------------|----------|

| PTPM749 A     | 0 to +70°C, Plastic Leaded Chip Carrier     | SOT261-3 |

| PTPM749 DB    | 0 to +70°C, Shrink Small Ouline Package     | SOT341-1 |

For compatible pointing device, contact:

| COMPANY           | CONTACT            | TELEPHONE      |  |

|-------------------|--------------------|----------------|--|

| Bokam Engineering | Ms. Jane Kamenster | (714) 513–2200 |  |

| CTS Corporation   | Mr. Dave Poole     | (219) 589–7169 |  |

IBM is a registered trademark, and TrackPoint is a trademark of IBM Corporation.

#### **PIN CONFIGURATION** P3.4/A4 [ 28 V<sub>CC</sub> 1 P3.3/A3 2 27 P3.5/A5 P3.2/A2/A10 3 26 P3.6/A6 25 P3.7/A7 P3.1/A1/A9 4 24 P0.4/PWM OUT P3.0/A0/A8 5 23 P0.3 P0.2 6 SHRINK SMALL 22 P1.7/T0/D7 P0.1/OE 7 OUTLINE 21 P1.6/INT1/D6 P0.0/ASEL 8 PACKAGE 20 P1.5/INT0/D5 RST 9 19 AV<sub>CC</sub> X2 10 18 AVss X1 11 17 P1.4/ADC4/D4 V<sub>SS</sub> 12 P1.0/ADC0/D0 13 16 P1.3/ADC3/D3 P1.2/ADC2/D2 P1.1/ADC1/D1 14 26 5 25 PLASTIC LEADED CARRIER 11 □ 19 18 12 Pin Function Pin Function P3.4/A4 15 P1.2/ADC2/D2 1 2 P3.3/A3 16 P1.3/ADC3/D3 P3.2/A2/A10 P1.4/ADC4/D4 3 17 P3.1/A1/A9 AVSS 18 4 P3.0/A0/A8 $AV_{CC}$ 5 19 P1.5/INT0/D5 6 P0.2 20 P0.1/OE P1.6/INT1/D6 7 21 P0.0/ASEL P1.7/T0/D7 8 22 P0.3 9 RST 23 P0.4/PWM OUT 10 X2 24 11 X1 25 P3.7/A7 12 26 P3.6/A6 VSS 13 P1.0/ADC0/D0 27 P3.5/A5 14 P1.1/ADC1/D1 28 V<sub>CC</sub> SU00692A

#### **PIN DESCRIPTION**

| MNEMONIC                      | PIN NO.         | TYPE   | NAME AND FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|-------------------------------|-----------------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| V <sub>SS</sub>               | 12              | I      | Circuit Ground Potential.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| V <sub>CC</sub>               | 28              | 1      | Supply voltage during normal, idle, and power-down operation.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| P0.0–P0.4                     | 8–6<br>23, 24   | I/O    | <b>Port 0:</b> Port 0 is a 5-bit bidirectional port. Port 0.0–P0.2 are open drain. Port 0.0–P0.2 pins that have 1s written to them float, and in that state can be used as high-impedance inputs. P0.3–P0.4 are bidirectional I/O port pins with internal pull-ups. These pins are driven low if the port register bit is written with a 0. The state of the pin can always be read from the port register by the program. Port 0.3 and 0.4 have internal pull-ups that function identically to port 3. Pins that have 1s written to them are pulled high by the internal pull-ups and can be used as inputs. |

|                               |                 |        | While P0.0 anbd P0.1 differ from "standard TTL" characteristics, they are close enough for the pins to still be used as general-purpose I/O.                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                               | 6<br>7          | I<br>I | <ul> <li>V<sub>PP</sub> (P0.2) – Programming voltage input.</li> <li>OE (P0.1) – Input which specifies verify mode (output enable).</li> <li>OE = 1 output enabled (verify mode).</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                               | 8               | I      | ASEL (P0.0) – Input which indicates which bits of the EPROM address are applied to port 3.<br>ASEL = 0 low address byte available on port 3.<br>ASEL = 1 high address byte available on port 3 (only the three least significant bits are used).                                                                                                                                                                                                                                                                                                                                                              |

| P1.0–P1.7                     | 13–17,<br>20–22 | I/O    | <b>Port 1:</b> Port 1 is an 8-bit bidirectional I/O port with internal pull-ups. Port 1 pins that have 1s written to them are pulled high by the internal pull-ups and can be used as inputs. P0.3–P0.4 pins are bidirectional I/O port pins with internal pull-ups. As inputs, port 1 pins that are externally pulled low will source current because of the internal pull-ups. (See DC Electrical Characteristics: I <sub>IL</sub> ). Port 1 also serves the special function features of the SC80C51 family as listed below:                                                                               |

|                               | 20              |        | INTO (P1.5): External interrupt.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                               | 21<br>22        |        | INT1 (P1.6): External interrupt.<br>T0 (P1.7): Timer 0 external input.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                               | 13–17           |        | <b>ADC0 (P1.0)–ADC4 (P1.4):</b> Port 1 also functions as the inputs to the five channel multiplexed A/D converter. These pins can be used as outputs only if the A/D function has been disabled. These pins can be used as digital inputs while the A/D converter is enabled.                                                                                                                                                                                                                                                                                                                                 |

|                               |                 |        | Port 1 serves to output the addressed EPROM contents in the verify mode and accepts as inputs the value to program into the selected address during the program mode.                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| P3.0–P3.7                     | 5–1,<br>27–25   | I/O    | <b>Port 3:</b> Port 3 is an 8-bit bidirectional I/O port with internal pull-ups. Port 3 pins that have 1s written to them are pulled high by the internal pull-ups and can be used as inputs. As inputs, port 3 pins that are externally being pulled low will source current because of the pull-ups. (See DC Electrical Characteristics: $I_{IL}$ ). Port 3 also functions as the address input for the EPROM memory location to be programmed (or verified). The 11-bit address is multiplexed into this port as specified by P0.0/ASEL.                                                                   |

| RST                           | 9               | I      | <b>Reset:</b> A high on this pin for two machine cycles while the oscillator is running resets the device. An internal diffused resistor to $V_{SS}$ permits a power-on RESET using only an external capacitor to $V_{CC}$ . After the device is reset, a 10-bit serial sequence, sent LSB first, applied to RESET, places the device in the programming state allowing programming address, data and $V_{PP}$ to be applied for programming or verification purposes. The RESET serial sequence must be synchronized with the X1 input.                                                                      |

| X1                            | 11              | I      | <b>Crystal 1:</b> Input to the inverting oscillator amplifier and input to the internal clock generator circuits. X1 also serves as the clock to strobe in a serial bit stream into RESET to place the device in the programming state.                                                                                                                                                                                                                                                                                                                                                                       |

| X2                            | 10              | 0      | Crystal 2: Output from the inverting oscillator amplifier.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| AV <sub>CC</sub> <sup>1</sup> | 19              | I.     | Analog supply voltage and reference input.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| AV <sub>SS</sub> <sup>1</sup> | 18              | I      | Analog supply and reference ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

NOTE:

1. AV<sub>SS</sub> (reference ground) must be connected to 0V (ground). AV<sub>CC</sub> (reference input) cannot differ from V<sub>CC</sub> by more than ±0.2V, and must be in the range 4.5V to 5.5V.

1451

Microcontroller with TrackPoint<sup>™</sup> microcode from IBM

### **TPM749**

#### **OSCILLATOR CHARACTERISTICS**

X1 and X2 are the input and output, respectively, of an inverting amplifier which can be configured for use as an on-chip oscillator.

To drive the device from an external clock source, X1 should be driven while X2 is left unconnected. There are no requirements on the duty cycle of the external clock signal, because the input to the internal clock circuitry is through a divide-by-two flip-flop. However, minimum and maximum high and low times specified in the data sheet must be observed.

#### **IDLE MODE**

The TPM includes the 80C51 power-down and idle mode features. In idle mode, the CPU puts itself to sleep while all of the on-chip peripherals except the A/D and PWM stay active. The functions that continue to run while in the idle mode are Timer 0, Timer I, and the interrupts. The instruction to invoke the idle mode is the last instruction executed in the normal operating mode before the idle mode is activated. The CPU contents, the on-chip RAM, and all of the special function registers remain intact during this mode. The idle mode can be terminated either by any enabled interrupt (at which time the process is picked up at the interrupt service routine and continued), or by a hardware reset which starts the processor in the same manner as a power-on reset. Upon powering-up the circuit, or exiting from idle mode, sufficient time must be allowed for stabilization of the internal analog reference voltages before an A/D conversion is started.

#### **POWER-DOWN MODE**

In the power-down mode, the oscillator is stopped and the instruction to invoke power-down is the last instruction executed. Only the contents of the on-chip RAM are preserved. A hardware reset is the only way to terminate the power-down mode. The control bits for the reduced power modes are in the special function register PCON.

#### Table 1. External Pin Status During Idle and Power-Down Modes

| MODE       | Port 0* | Port 1 | Port 2 |

|------------|---------|--------|--------|

| Idle       | Data    | Data   | Data   |

| Power-down | Data    | Data   | Data   |

Except for PWM output (P0.4).

#### I/O Ports

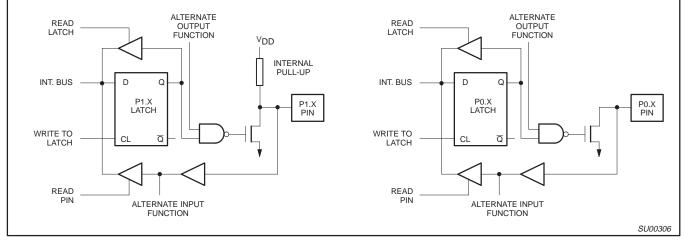

The I/O pins provided by the TPM consist of port 0, port 1, and port 3.

#### Port 0

Port 0 is a 5-bit bidirectional I/O port and includes alternate functions on some pins of this port. Pins P0.3 and P0.4 are provided with internal pullups while the remaining pins (P0.0, P0.1, and P0.2) have open drain output structures. The alternate function for port P0.4 is PWM output.

If the alternate function PWM is not being used, then this pin may be used as an I/O port.

#### Port 1

Port 1 is an 8-bit bidirectional I/O port whose structure is identical to the 80C51, but also includes alternate input functions on all pins. The alternate pin functions for port 1 are:

P1.0-P1.4 - ADC0-ADC4 - A/D converter analog inputs P1.5 INT0 - external interrupt 0 input P1.6 INT1 - external interrupt 1 input P1.7 - T0 - timer 0 external input

If the alternate functions  $\overline{INT0}$ ,  $\overline{INT1}$ , or T0 are not being used, these pins may be used as standard I/O ports. It is necessary to connect AV<sub>CC</sub> and AV<sub>SS</sub> to V<sub>CC</sub> and V<sub>SS</sub>, respectively, in order to use P1.5, P1.6, and P1.7 pins as standard I/O pins. When the A/D converter is enabled, the analog channel connected to the A/D may not be used as a digital input; however, the remaining analog inputs may be used as digital inputs. They may not be used as digital outputs. While the A/D is enabled, the analog inputs are floating.

#### Port 3

Port 3 is an 8-bit bidirectional I/O port whose structure is identical to the 80C51. Note that the alternate functions associated with port 3 of the 80C51 have been moved to port 1 of the TPM (as applicable). See Figure 1 for port bit configurations.

Figure 1. Port Bit Latches and I/O Buffers

### **TPM749**

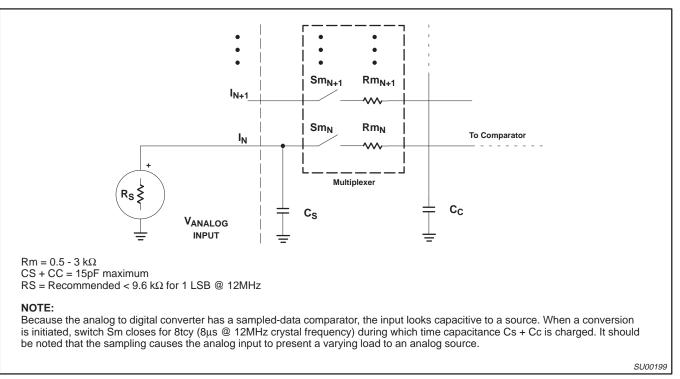

Figure 2. A/D Input: Equivalent Circuit

#### A/D CONVERTER PARAMETER DEFINITIONS

The following definitions are included to clarify some specifications given and do not represent a complete set of A/D parameter definitions.

#### Absolute Accuracy Error

Absolute accuracy error of a given output is the difference between the theoretical analog input voltage to produce a given output and the actual analog input voltage required to produce the same code. Since the same output code is produced by a band of input voltages, the "required input voltage" is defined as the midpoint of the band of input voltage that will produce that code. Absolute accuracy error not specified with a code is the maximum over all codes.

#### Nonlinearity

If a straight line is drawn between the end points of the actual converter characteristics such that zero offset and full scale errors are removed, then non-linearity is the maximum deviation of the code transitions of the actual characteristics from that of the straight line so constructed. This is also referred to as relative accuracy and also integral non-linearity.

#### **Differential Non-Linearity**

Differential non-linearity is the maximum difference between the actual and ideal code widths of the converter. The code widths are the differences expressed in LSB between the code transition points, as the input voltage is varied through the range for the complete set of codes.

#### **Gain Error**

Gain error is the deviation between the ideal and actual analog input voltage required to cause the final code transition to a full-scale output code after the offset error has been removed. This may sometimes be referred to as full scale error.

#### Offset Error

Offset error is the difference between the actual input voltage that causes the first code transition and the ideal value to cause the first code transition. This ideal value is 1/2 LSB above  $V_{ref-}$ .

#### **Channel to Channel Matching**

Channel to channel matching is the maximum difference between the corresponding code transitions of the actual characteristics taken from different channels under the same temperature, voltage and frequency conditions.

#### Crosstalk

Crosstalk is the measured level of a signal at the output of the converter resulting from a signal applied to one deselected channel.

#### **Total Error**

Maximum deviation of any step point from a line connecting the ideal first transition point to the ideal last transition point.

#### **Relative Accuracy**

Relative accuracy error is the deviation of the ADC's actual code transition points from the ideal code transition points on a straight line which connects the ideal first code transition point and the final code transition point, after nullifying offset error and gain error. It is generally expressed in LSBs or in percent of FSR.

**TPM749**

### ABSOLUTE MAXIMUM RATINGS<sup>1, 3, 4</sup>

| PARAMETER                                           | RATING                        | UNIT |

|-----------------------------------------------------|-------------------------------|------|

| Storage temperature range                           | -65 to +150                   | °C   |

| Voltage from $V_{CC}$ to $V_{SS}$                   | -0.5 to +6.5                  | V    |

| Voltage from any pin to $V_{SS}$ (except $V_{PP}$ ) | −0.5 to V <sub>CC</sub> + 0.5 | V    |

| Power dissipation                                   | 1.0                           | W    |

| Voltage from V_PP pin to V_SS                       | -0.5 to + 13.0                | V    |

NOTES ON PAGE 1455.

### DC ELECTRICAL CHARACTERISTICS

$T_{amb}$  = 0°C to +70°C, AV\_{CC} = 5V ±5, AV\_{SS} = 0V^4  $V_{CC}$  = 5V ± 10%, V\_{SS} = 0V

|                                                        |                                                                                                                                      | TEST                                                                                       |                                                         | LIMITS <sup>4</sup> |                                                                         |                  |

|--------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|---------------------------------------------------------|---------------------|-------------------------------------------------------------------------|------------------|

| SYMBOL                                                 | PARAMETER                                                                                                                            | CONDITIONS                                                                                 | MIN                                                     | TYP <sup>1</sup>    | МАХ                                                                     | UNIT             |

| I <sub>CC</sub>                                        | Supply current (see Figure 5)                                                                                                        |                                                                                            |                                                         |                     |                                                                         | 1                |

| Inputs                                                 | •                                                                                                                                    | -                                                                                          | -                                                       | •                   | -                                                                       | •                |

| V <sub>IL</sub><br>V <sub>IH</sub><br>V <sub>IH1</sub> | Input low voltage<br>Input high voltage, except X1, RST<br>Input high voltage, X1, RST                                               |                                                                                            | -0.5<br>0.2V <sub>CC</sub> +0.9<br>0.7V <sub>CC</sub>   |                     | 0.2V <sub>CC</sub> -0.1<br>V <sub>CC</sub> +0.5<br>V <sub>CC</sub> +0.5 | V<br>V<br>V      |

| V <sub>IL1</sub><br>V <sub>IH2</sub>                   | P0.2<br>Input low voltage<br>Input high voltage                                                                                      |                                                                                            | -0.5<br>0.7V <sub>CC</sub>                              |                     | 0.3V <sub>CC</sub><br>V <sub>CC</sub> +0.5                              | V<br>V           |

| Outputs                                                | Output low values parts 1, 2, 0,2, and 0,4                                                                                           |                                                                                            |                                                         |                     |                                                                         | 1                |

| V <sub>OL</sub><br>V <sub>OL1</sub>                    | Output low voltage, ports 1, 3, 0.3, and 0.4<br>(PWM disabled)<br>Output low voltage, port 0.2                                       | l <sub>OL</sub> = 1.6mA <sup>2</sup><br>l <sub>OL</sub> = 3.2mA <sup>2</sup>               |                                                         |                     | 0.45<br>0.45                                                            | V<br>V           |

| V <sub>OH</sub>                                        | Output high voltage, ports 1, 3, 0.3, and 0.4<br>(PWM disabled)                                                                      | $I_{OH} = -60\mu A,$<br>$I_{OH} = -25\mu A$<br>$I_{OH} = -10\mu A$<br>$I_{OH} = -400\mu A$ | 2.4<br>0.75V <sub>CC</sub><br>0.9V <sub>CC</sub><br>2.4 |                     |                                                                         | V<br>V<br>V<br>V |

| V <sub>OH2</sub>                                       | Output high voltage, P0.4 (PWM enabled)                                                                                              | I <sub>OH</sub> = -40μA                                                                    | 0.9V <sub>CC</sub>                                      |                     |                                                                         | V                |

| V <sub>OL2</sub><br>C                                  | Port 0.0 and 0.1 – Drivers<br>Output low voltage<br>Driver, receiver combined:<br>Capacitance                                        | I <sub>OL</sub> = 3mA<br>(over V <sub>CC</sub> range)                                      |                                                         |                     | 0.4<br>10                                                               | V<br>pF          |

| IIL                                                    | Logical 0 input current,                                                                                                             | V <sub>IN</sub> = 0.45V                                                                    |                                                         |                     | -50                                                                     | μA               |

| I <sub>TL</sub>                                        | ports 1, 3, 0.3, and 0.4 (PWM disabled) <sup>11</sup><br>Logical 1 to 0 transition current,<br>ports 1, 3, 0.3 and 0.4 <sup>11</sup> | $V_{IN} = 2V$                                                                              |                                                         |                     | -650                                                                    | μA               |

| I <sub>LI</sub>                                        | Input leakage current, port 0.0, 0.1 and 0.2                                                                                         | $0.45 < V_{IN} < V_{CC}$                                                                   |                                                         |                     | ±10                                                                     | μA               |

| R <sub>RST</sub>                                       | Reset pull-down resistor                                                                                                             |                                                                                            | 25                                                      |                     | 175                                                                     | kΩ               |

| C <sub>IO</sub>                                        | Pin capacitance                                                                                                                      | Test freq = 1MHz,<br>T <sub>amb</sub> = 25°C                                               |                                                         |                     | 10                                                                      | pF               |

| I <sub>PD</sub>                                        | Power-down current <sup>5</sup>                                                                                                      | $V_{CC} = 2 \text{ to } 5.5 \text{V}$<br>$V_{CC} = 2 \text{ to } 6.0 \text{V}$             |                                                         |                     | 50                                                                      | μΑ               |

NOTES ON FOLLOWING PAGE.

### TPM749

### DC ELECTRICAL CHARACTERISTICS (Continued)

$T_{amb} = 0^{\circ}C$  to +70°C,  $AV_{CC} = 5V \pm 5$ ,  $AV_{SS} = 0V^4$

$V_{CC} = 5V \pm 10\%, V_{SS} = 0V$

|                  | TEST LIMITS <sup>4</sup>                               |                             |                      |                  |                       |      |

|------------------|--------------------------------------------------------|-----------------------------|----------------------|------------------|-----------------------|------|

| SYMBOL           | PARAMETER                                              | CONDITIONS                  | MIN                  | TYP <sup>1</sup> | MAX                   | UNIT |

| Analog Inp       | <b>buts</b> (A/D guaranteed only with quartz window co | overed.)                    |                      | -<br>-           |                       | -    |

| AV <sub>CC</sub> | Analog supply voltage <sup>10</sup>                    | $AV_{CC} = V_{CC} \pm 0.2V$ | 4.5                  |                  | 5.5                   | V    |

| Al <sub>CC</sub> | Analog operating supply current                        | AV <sub>CC</sub> = 5.12V    |                      |                  | 3 <sup>9</sup>        | mA   |

| AV <sub>IN</sub> | Analog input voltage                                   |                             | AV <sub>SS</sub> 0.2 |                  | AV <sub>CC</sub> +0.2 | V    |

| C <sub>IA</sub>  | Analog input capacitance                               |                             |                      |                  | 15                    | pF   |

| t <sub>ADS</sub> | Sampling time                                          |                             |                      |                  | 8t <sub>CY</sub>      | s    |

| t <sub>ADC</sub> | Conversion time                                        |                             |                      |                  | 40t <sub>CY</sub>     | s    |

| Analog Inp       | outs (A/D guaranteed only with quartz window co        | overed.) (Continued)        |                      |                  |                       |      |

| R                | Resolution                                             |                             |                      |                  | 8                     | bits |

| E <sub>RA</sub>  | Relative accuracy                                      |                             |                      |                  | ±1                    | LSB  |

| OS <sub>e</sub>  | Zero scale offset                                      |                             |                      |                  | ±1                    | LSB  |

| G <sub>e</sub>   | Full scale gain error                                  |                             |                      |                  | 0.4                   | %    |

| M <sub>CTC</sub> | Channel to channel matching                            |                             |                      |                  | ±1                    | LSB  |

| Ct               | Crosstalk                                              | 0–100kHz                    |                      |                  | -60                   | dB   |

NOTES:

1. Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any conditions other than those described in the AC and DC Electrical Characteristics section of this specification is not implied.

2. Under steady state (non-transient) conditions, I<sub>OL</sub> must be externally limited as follows:

Maximum I<sub>OL</sub> per port pin:

Maximum IOL per 8-bit port: 26mA

Maximum total IOL for all outputs: 67mA

If IOL exceeds the test condition, VOL may exceed the related specification. Pins are not guaranteed to sink current greater than the listed test conditions.

This product includes circuitry specifically designed for the protection of its internal devices from the damaging effects of excessive static 3. charge. Nonetheless, it is suggested that conventional precautions be taken to avoid applying greater than the rated maxima.

4. Parameters are valid over operating temperature range unless otherwise specified. All voltages are with respect to V<sub>SS</sub> unless otherwise noted.

5. Power-down I<sub>CC</sub> is measured with all output pins disconnected; port 0 = V<sub>CC</sub>; X2, X1 n.c.; RST = V<sub>SS</sub>. 6. I<sub>CC</sub> is measured with all output pins disconnected; X1 driven with t<sub>CLCH</sub>, t<sub>CHCL</sub> = 5ns, V<sub>IL</sub> = V<sub>SS</sub> + 0.5V, V<sub>IH</sub> = V<sub>CC</sub> - 0.5V; X2 n.c.; RST = port 0 =  $V_{CC}$ . I<sub>CC</sub> will be slightly higher if a crystal oscillator is used.

7. Idle I<sub>CC</sub> is measured with all output pins disconnected; X1 driven with  $t_{CLCH}$ ,  $t_{CHCL}$  = 5ns,  $V_{IL}$  =  $V_{SS}$  + 0.5V,  $V_{IH}$  =  $V_{CC}$  - 0.5V; X2 n.c.; port  $0 = V_{CC}$ ; RST = V<sub>SS</sub>.

Load capacitance for ports = 80pF. 8.

9. The resistor ladder network is not disconnected in the power down or idle modes. Thus, to conserve power, the user may remove AV<sub>CC</sub>.

10. If the A/D function is not required, or if the A/D function is only needed periodically, AV<sub>CC</sub> may be removed without affecting the operation of the digital circuitry. Contents of ADCON and ADAT are not guaranteed to be valid. If AV<sub>CC</sub> is removed, the A/D inputs must be lowered to less than 0.5V. Digital inputs on P1.0-P1.4 will not function normally.

11. These parameters do not apply to P1.0-P1.4 if the A/D function is enabled.

**TPM749**

### AC ELECTRICAL CHARACTERISTICS

$T_{amb}$  = 0°C to +70°C,  $V_{CC}$  = 5V ±10%,  $V_{SS}$  = 0V^4,  $^8$

|                           |                       | 12MHz CLOCK |     | VARIABLE CLOCK |     |      |

|---------------------------|-----------------------|-------------|-----|----------------|-----|------|

| SYMBOL                    | PARAMETER             | MIN         | MAX | MIN            | МАХ | UNIT |

| 1/t <sub>CLCL</sub>       | Oscillator frequency: |             |     | 3.5            | 12  | MHz  |

| External Clock (Figure 3) |                       |             |     |                |     |      |

| t <sub>CHCX</sub>         | High time             | 20          |     | 20             |     | ns   |

| t <sub>CLCX</sub>         | Low time              | 20          |     | 20             |     | ns   |

| t <sub>CLCH</sub>         | Rise time             |             | 20  |                | 20  | ns   |

| t <sub>CHCL</sub>         | Fall time             |             | 20  |                | 20  | ns   |

### **EXPLANATION OF THE AC SYMBOLS**

Each timing symbol has five characters. The first character is always 't' (= time). The other characters, depending on their positions, indicate the name of a signal or the logical status of that signal. The designations are:

- C Clock

- D Input data

- H Logic level high

- L Logic level low

- Q Output data

- T Time

- V Valid

- X No longer a valid logic level

- Z Float

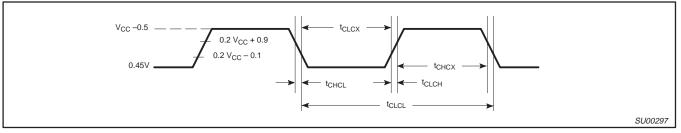

#### Figure 3. External Clock Drive

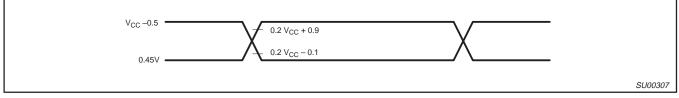

Figure 4. AC Testing Input/Output

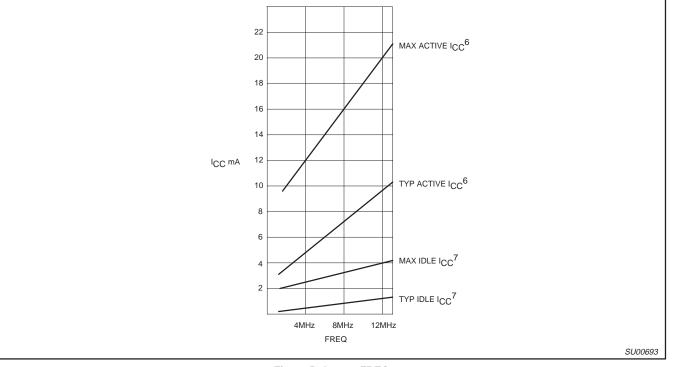

Figure 5.  $I_{CC}$  vs. FREQ Maximum  $I_{CC}$  values taken at  $V_{CC}$  = 5.5V and worst case temperature. Typical  $I_{CC}$  values taken at  $V_{CC}$  = 5.0V and 25°C. Notes 6 and 7 refer to AC Electrical Characteristics.

#### PLCC28: plastic leaded chip carrer; 28 leads; pedestal SOT261-3 ¢ е<sub>D</sub> еE 🛛 у X A 25 19 ΖE 18 26 ₽wM C D 28 b $H_{F}$ E ۱Ð ł pin 1 index þ C е Γ Α4 12 k 4 5 11 = v (M) A L ΖD е detail X В D $^{\rm H}{ m D}$ = v 🕅 B 5 10 mm Ω scale DIMENSIONS (millimetre dimensions are derived from the original inch dimensions) Z<sub>D</sub><sup>(1)</sup> $Z_E^{(1)}$ A<sub>1</sub> $A_4$ D<sup>(1)</sup> E<sup>(1)</sup> UNIT Α b<sub>1</sub> е $H_D$ $H_{\mathsf{E}}$ k øj ۷ w У β Α3 bp е<sub>D</sub> е<sub>Е</sub> Lp min. max. max. max 4.57 0.53 0.81 11.58 11.58 10.92 10.92 12.57 12.57 1.22 5.69 1.44 0.18 0.10 mm 0.13 0.25 3.05 1.27 0.18 2.06 2.06 4.19 0.33 0.66 11.43 11.43 9.91 9.91 12.32 12.32 1.07 5.54 1.02 45° 0.180 0.165 0.021 0.032 0.456 0.456 0.430 0.430 0.495 0.495 0.048 0.224 0.057 0.12 0.05 inches 0.005 0.01 0.007 0.007 0.004 0.081 0.081 0.013 0.026 0.450 0.450 0.390 0.390 0.485 0.485 0.042 0.218 0.040

#### Note

1. Plastic or metal protrusions of 0.01 inches maximum per side are not included.

| OUTLINE  |     | REFER    | ENCES |            |                                  |  |

|----------|-----|----------|-------|------------|----------------------------------|--|

| VERSION  | IEC | JEDEC    | EIAJ  | PROJECTION | ISSUE DATE                       |  |

| SOT261-3 |     | MO-047AB |       |            | <del>-92-11-17</del><br>95-02-25 |  |

### **TPM749**

#### 1996 May 01

NOTES